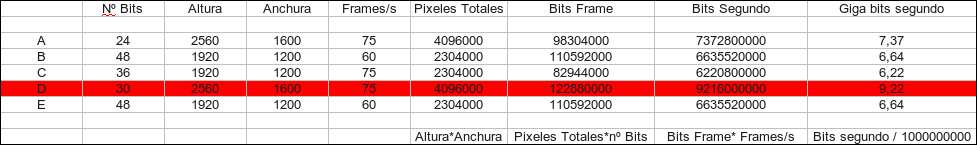

1. La interfaz HDMI 1.3 permite para el vídeo una máxima velocidad de transferencia de 8.16 Gbit/s. Se denomina Deep Color cuando el color de los pixels de una imagen se codifica con 30, 36 o 48 bits, si se codifica con 24 bits se denomina True Color. ¿Cuál de las siguientes resoluciones no funcionaría en esta interfaz?

A: 24bits, 2560x1600p, 75 frames/s

B: 48bits, 1920x1200p, 60 frames/s

C: 36bits, 1920x1200p, 75 frames/s

D: 30bits, 2560x1600p, 75 frames/s

E: 48bits, 1920x1200p, 60 frames/s

explicación

2. El AGP 8x es un bus paralelo con las siguientes características: bus de datos de 32 bits, frecuencia de reloj 66 MHz y transmite 4 datos por ciclo de reloj. ¿Cuál es su velocidad de transferencia?

A: 2112 MB/s

B: 4224 MB/s

C: 1056 MB/s

D: 528 MB/s

E: 8448 MB/s

3 Un bus serie síncrono tiene una única línea de datos, transfiere 4 bits por ciclo de reloj, y trabaja a una frecuencia de 1GHz. ¿Cuál es la velocidad de transferencia?

A: 250 MBytes/s

B: 500 MBytes/

C: 125 MBytes/s

D: 2×2^30 bits/s

E: 1000 MBytes/s

en cada ciclo transfiere 4 bits y la frecuencia es de 1GHz que es lo mismo que 1000000000 herzios por lo tanto en un segundo se producen 1000000000 ciclos y en cada ciclo se transfieren 4bits

4*1000000000=4000000000 bits/s = 500000000 bytes/s = 500000 Kbytes/s = 500 Mbytes/s

4. Una computadora tiene un microprocesador Pentium 4 cuyo bus de direcciones tiene 36 bits, y su memoria principal de 2 GiBytes (que empieza en la dirección 0). Indica la primera y última dirección que el micro puede direccionar, y la primera y última dirección que realmente direcciona por la limitación de la memoria principal.

A: 00000000h FFFFFFFFh 00000000h 07FFFFFFh

B: 00000000h FFFFFFFFh 00000000h 0FFFFFFFh

C: 000000000h FFFFFFFFFh 000000000h 0FFFFFFFFh

D: 000000000h FFFFFFFFFh 000000000h 07FFFFFFFh

E: 0000000000h FFFFFFFFFFh 0000000000h 0FFFFFFFFFh

Empezamos por la direccion que el micro puede direccionar.

el bus de direcciones tiene 36bits escribimos 36 unos

111111111111111111111111111111111111

los separamos en grupos de 4

1111 1111 1111 1111 1111 1111 1111 1111 1111

pasamos cada grupo de 4 a hexadecimal

1111 1111 1111 1111 1111 1111 1111 1111 1111

F F F F F F F F F

por lo tanto la direccion mas alta para direccionar con 36bits es:

FFFFFFFFFh

si cambiamos las Fs por 0s obtenemos la dirección mas baja

000000000h

para la memoria principal empezamos:

2 GiBytes =2*1024 MiBytes = 2*1024*¹024 KiBytes = 2*1024*1024*1024 Bytes = 2*1024*1024*1024 Bits = 2^31 bits por lo tanto necesitamos 31bits para representar 2GiBytes.

asi que escribimos 31 unos y los agrupamos en grupos de 4

0111 1111 1111 1111 1111 1111 1111 1111 y los pasamos a hexadecimal

7 F F F F F F F

7FFFFFFFh

00000000h

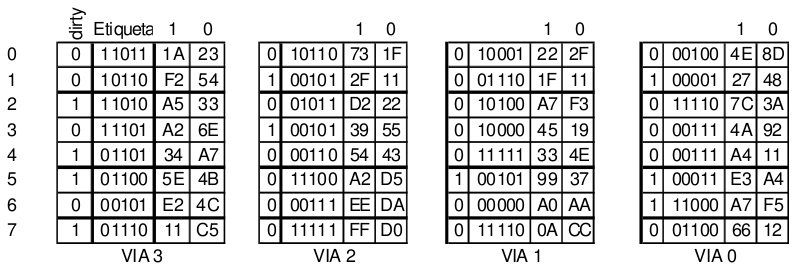

Se ha diseñado la memoria caché de un computador siguiendo la organización de la figura, en la cual se muestra además el estado de la misma en un instante. Las direcciones de memoria principal tienen ceros adicionales a la izquierda.

5. ¿Qué dato proporcionará la caché a la CPU cuando ésta lea la dirección 0052h?

explicación:

Partimos de la dirección 0052h

pasamos la dirección a binario

Hexadecimal–> 0 0 5 2

Binario –> 0000 0000 0101 0010

entonces nuestra dirección de memoria es:

01010010

segmentamos la dirección de memoria en los campos corresposdientes

Etiqueta Indice Palabra

0101 001 0

La buscamos en la tabla segun los datos segmentados

Indice 1 Etiqueta 00101 Palabra 0

Valor 11h

6. ¿Qué dirección de memoria principal está almacenada en la línea 7, vía 3, posición 0 ?

miramos los datos en la tabla

indice etiqueta posición

7 (111) 01110 0

los pasamos a binario y los ordenamos de la misma manera que se almacenan osea etiqueta, indice y posicion

etiqueta indice posicion

01110 111 0

agrupamos los bits en grupos de cuatro

0 1110 1110

los pasamos a hexadecimal

00EEh

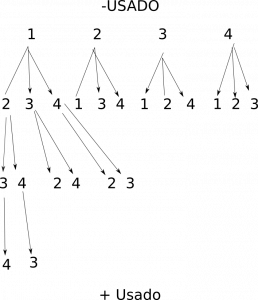

7. Si quisiéramos implementar un algoritmo de reemplazo LRU, ¿cuántos bits necesitaríamos como mínimo para guardar el orden de todas las vías de todos los conjuntos?

A: 48bits

B: 32bits

C: 10bits

D: 40bits

E: 56bits

para cada conjunto tenemos que guardar el orden de cada linea es este esquema vemos la estructura de las posibles combinaciones

asi que una linea genera 4*3*2*1=24 combinaciones para lo cual necesitamos 5bits 2^5 (porque 2^4 es < que 24)

asi que una linea genera 4*3*2*1=24 combinaciones para lo cual necesitamos 5bits 2^5 (porque 2^4 es < que 24)

si tenemos 8 lineas y necesitamos 5bits por linea = 8*5= 40bits

8. Supongamos que cada línea tiene un contador. Cuando se hace referencia a una línea su contador asociado se pone a cero. Después los contadores de todas las líneas se incrementan en uno. ¿Para qué puede ser utilizado este método? Para implementar:

A: Alg Reemplazo LRU

B: Alg Reemplazo LFU

C: Post Escritura

D: Escritura inmediata

E: Ninguno de los anteriores

Un disco duro que gira a 12000 rpm tiene 100 sectores por pista y cada sector tiene 1000 Bytes, de los cuales sólo 512 son de datos (el resto son huecos, identificador de sector y código de detección y corrección de errores). El tiempo medio de búsqueda es de 1 ms.

9. Se ordena una operación sobre un fichero almacenado en 5 sectores consecutivos de una pista y en otros 3 sectores consecutivos en otra pista. ¿Qué tiempo transcurre hasta que se lee el último byte del fichero?

A: 7.4ms

B: 3.9ms

C: 10.9ms

D: 3.55ms

E: 3.75ms

Sabemos que es disco duro gira a 12000 rpm (Revoluciones por minuto) o lo que es lo mismo 12000/60 rps (Revoluciones por segundo)

en un segundo nuestro disco duro dara 200 vueltas

y daremos una vuelta en 1segundo /200 vueltas= 0,005 segundos = 5 milisegundos

en 5 milisegundos leeremos 100 sectores por lo que en 5/100 milisegundos leeremos un sector o lo que es lo mismo leemos 5ms que tardamos en leer un sector

tendremos que realizar 2 tandas una para los 5 sectores consecutivos y otra para los 3 sectores consecutivos.

- 5 sectores consecutivos

- 1ms para buscar la pista

- 2,5 milisegundos para encontrar el primer sector (lo que tardamos en dar media vuelta)

- 5*0,05ms=0,25ms tiempo que tardamos en leer los 5 sectores

- Total: 1+2,5+0,25=3,75ms

- 3 sectores consecutivos

- 1ms para buscar la pista

- 2,5 milisegundos para encontrar el primer sector (lo que tardamos en dar media vuelta)

- 3*0,05ms = 0,15ms tiempo que tardamos en leer los 3 sectores

- Total:1+2,5+0,15=3,65ms

El tiempo necesario para leer el fichero sera= 3,75ms + 3,65ms = 7,4ms

10. ¿Cada cuánto tiempo envía el disco duro un dato a su módulo de entrada salida?

A: 10ns

B: 20ns

C: 50ns

D: 25ns

E: 30ns

El disco duro manda los 1000 bytes por cada sector

Del apartado anterior sabemos que tardamos 0,05ms en leer un sector

0,05/1000= 0,00005 ms que tardamos en leer un byte= 50ns

11. Si utilizamos interrupciones, el registro de datos o buffer de datos tiene de tamaño 2 bytes, se genera una interrupción sólo cuando el buffer se llena, y la rutina de servicio dura 10 ns. ¿Cuánto tiempo dedica la CPU a otras tareas entre la interrupción número 2 y la 3?

A: 90ns

B: 80ns

C: 70ns

D: 110ns

E: 120ns

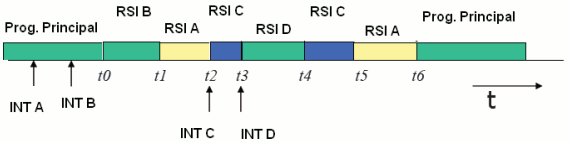

12. En t0 se permiten las interrupciones (hasta ese momento aunque se produjeran interrupciones, sus rutinas no se ejecutan). Las interrupciones son anidadas. ¿Qué afirmaciones son correctas?

A:B tiene más prioridad que A, y D más que A, y A más que C

B:A tiene más prioridad que B, y D más que C, y C más que A

C:B tiene más prioridad que A, y B más que C, y A más que C

D:B tiene más prioridad que A, y D más que C, y C más que A

E:B tiene más prioridad que C, y A más que C, y C más que D

13. Después de ejecutar este programa, ¿cuál es el contenido de la dir F000h de M.P.?

[ASM]

Mvi a,70h

Sta F000h

Lxi h,F000h

Inx h

Inr m

Dcx h

Inr m

Inx h

Inr m

Dcx h

Inr m

Inr m

[/ASM]

A: 70h

B: 75h

C: 72h

D: 73h

E: 68h

14. Todas las direcciones de MP valen 04h. Después de ejecutar el siguiente programa, que dirección de memoria vale 08h?

[ASM]

Lxi h,F020h

Mov a,m

Inr m

Inx h

Inr h

Dcr l

Add m

Mov m,a

[/ASM]

A: F020h

B: F120h

C: F121h

D: F220h

E: F021h

15. Después de ejecutar el siguiente programa, ¿qué línea del puerto B cambia de estado?

[ASM]

Mvi A, 90h

Out 0Bh

Mvi A, 5Fh

Out 09h

Ani EEh

Ori 05h

Out 09h

[/ASM]

A: Linea 3

B: Linea 6

C: Linea 4

D: Linea 2

E: Linea 0

16. Una subrutina tiene el siguiente código. Cuando finalice la rutina, cual será la siguiente instrucción que se ejecute?

[ASM]

Push h

Lxi h, 4000h

Pop h

Pop h

Lxi h,2000h

Push h

Push h

Lxi h, 1000h

Pop h

Push h

Lxi h, 3000h

Pop h

Ret

[/ASM]

A: Será la siguiente instrucción al call que llamó a la rutina

B: Será la 1000h

C: Será la 2000h

D: Será la 3000h

E: Será la 4000h